Amélioration d’un réseau de neurones à convolution sur cible FPGA

L’intelligence artificielle est de plus en plus présente dans notre quotidien. Elle est majoritairement utilisée pour traiter des données de masse (réseaux sociaux, bots, assistance, reconnaissance d’image, etc.). Une partie de ces intelligences artificielles sont des algorithmes d’apprentissage profond, ou Deep Learning. Leur particularité est de pouvoir apprendre seuls la différence entre deux objets (ou une autre tâche).

Le Deep Learning est devenu un axe de recherches majeur pour un grand nombre d’entreprises et de laboratoires. Chez ELSYS Design, nous cherchons à déterminer l’efficacité d’un réseau de neurones à convolution sur cible FPGA : c’était l’objet du stage réalisé par Romain et Florian.

Contexte

Les réseaux de neurones à convolution sont de plus en plus utilisés pour détecter des objets dans des images ; des visages, ou des nuages par exemple. Néanmoins, il est nécessaire d’avoir un bon ordinateur avec beaucoup de RAM (Random Access Memory) et/ou un GPU (Graphics Processing Unit) pour pouvoir traiter les images.

Ce moyen de traitement n’est pas optimal car il faut dans un premier temps transférer les images à l’ordinateur avant d’obtenir le résultat. De plus, le traitement de l’image prend du temps et de nombreuses ressources. Il est donc naturel de se tourner vers un développement matériel pour permettre à la fois d’accélérer le processus, d’en diminuer le coût en ressources et de permettre un traitement embarqué.

Descriptif du stage

C’est dans ce contexte que se situe le stage. Son objectif était d’implémenter un CNN (Convolutional Neural Network) à détection sur cible FPGA pour pouvoir distinguer quel objet est situé dans une image.

Cet algorithme devait être accompagné d’un flux vidéo en temps réel relié à une caméra. Le tout devait être embarqué sur FPGA Xilinx ZCU104.

Florian a été chargé de réaliser le flux vidéo et Romain le réseau neuronal.

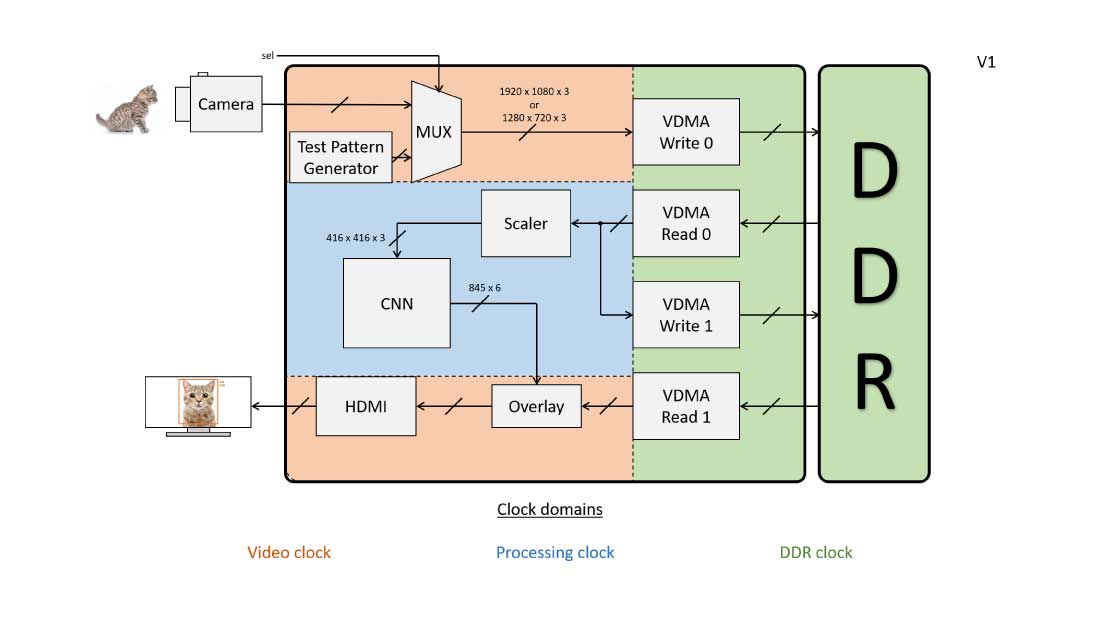

Architecture

Le réseau neuronal constitue le cœur de l’architecture, la chaine de traitement vidéo vient se greffer autour. On réalise d’abord l’acquisition des images via une caméra USB, pour ensuite les transférer au réseau afin qu’il puisse les traiter. Après l’opération de détection, on superpose sur l’image le résultat, soit la mise en évidence des objets, leurs natures, ainsi que la fiabilité statistique. Finalement on affiche l’image et son overlay, par l’intermédiaire d’un port HDMI.

La réalisation

Le réseau neuronal qui a été réalisé est un réseau neuronal à détection connu sous le nom de YOLO (You Only Look Once) ; « à détection » signifie que le réseau est également capable de détecter de façon grossière la position des objets dans l’image en plus de les reconnaitre.

Il est composé de 22 couches de convolution, ce qui le rend particulièrement complexe. L’implémentation du code C++ a été réalisée en synthèse de haut niveau grâce à l’outil Vivado HLS, ce qui a permis de se concentrer majoritairement sur la compréhension et l’implémentation de l’algorithme.

Pour Romain, « réaliser ce projet m’a donné l’opportunité de me familiariser avec les réseaux neuronaux et leur fonctionnement. Il m’a également permis de développer des compétences en synthèse de haut niveau et notamment de continuer à penser au matériel généré lorsque je code en C++ ».

Florian estime pour sa part qu’il s’agit d’« un stage très riche et formateur, durant lequel j’ai pu approfondir mes connaissances en matière de design FPGA et de traitement vidéo. J’ai le sentiment d’avoir acquis de bons réflexes de design, et d’avoir consolidé mes compétences en développement VHDL ainsi qu’en conduite de projet.

A noter que ce stage constitue la première étape du projet Forty-Two, interne à ELSYS Design, qui a pour finalité la comparaison entre un CNN à détection et un BNN (Binary Neural Network) à détection, le tout sur cible FPGA. Rendez-vous en 2021 pour découvrir la suite !

Envie de réaliser votre stage de fin d’études chez ELSYS Design ? Alors rendez-vous sur notre site emploi pour consulter nos offres, ou déposer une candidature spontanée !